### CrossMan

### JMR EARLY CAREER SCHOLARS IN MATERIALS SCIENCE ANNUAL ISSUE

# Graphene field-effect transistor application-electric band structure of graphene in transistor structure extracted from quantum capacitance

Kosuke Nagashio<sup>a)</sup>

Department of Materials Engineering, The University of Tokyo, Tokyo 113-8656, Japan; and PRESTO, Japan Science and Technology Agency (JST), Tokyo 113-8656, Japan

(Received 6 June 2016; accepted 8 September 2016)

Recently, various two-dimensional (2D) materials, such as graphene, transition metal dichalcogenides and so on, have attracted much attention in electron device research. The most important characteristic of graphene is its highest mobility of all semiconductor channels at room temperature. However, it is obvious that more than a good mobility characteristic is required to realize the field effect transistor (FET), and intense arguments from various points of view are necessary. In this paper, the issues with Si-metal oxide semiconductor FETs (Si-MOSFET) and the advantage of 2D materials are discussed. The present state of graphene FETs with respect to gate stack formation and band gap engineering is reported. Moreover, based on the density of states (DOS) of graphene extracted using the quantum capacitance ( $C_Q$ ) measurement, it is shown that the electric band structure of graphene in contact with gate insulators or metal electrode deviates from its intrinsic band structure.

Kosuke Nagashio

Kosuke Nagashio received the BE degree in Materials Science & Engineering from Kyoto University in 1997 and the ME and PhD degrees in Materials Engineering from The University of Tokyo in 1999 and 2002, respectively. He is currently an Associate Professor with the Department of Materials Engineering, The University of Tokyo. His research interests presently focus on the carrier transport for layered materials and the crystal growth. Dr Nagashio is a member of the Japan Society of Applied Physics (JSAP), the Japan Institute of Metals (JIM), the Materials Research Society (MRS) and the IEEE Electron Device Society (EDS).

## I. ISSUES WITH SI-MOSFET AND THE ADVANTAGE OF 2D CHANNELS

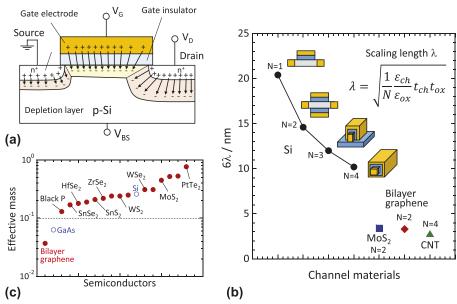

The issues with the miniaturization of Si-MOSFETs are generically called short channel effects. When the source and drain depletion regions become comparable in length with the channel length, as shown in Fig. 1(a), the drain bias weakens the gate bias, which leads to a drastic increase in the off-current. Based on an analysis of the distribution of the electrical potential in the channel region, it is widely known that the short channel effect can be neglected when the channel length is  $\sim 6$  times longer than the scaling length,  $\lambda = \sqrt{(\varepsilon_{\rm ch} t_{\rm ch} t_{\rm ox})/(N\varepsilon_{\rm ox})},^{2,3}$  where  $\varepsilon_{\rm ch}$ ,  $\varepsilon_{\rm ox}$ ,  $t_{\rm ch}$ , and  $t_{\rm ox}$  are the dielectric constants for the channel, the gate insulator, the thickness of the channel, and the gate oxide,

Contributing Editor: Mauricio Terrones <sup>a)</sup>Address all correspondence to this author. e-mail: nagashio@material.t.u-tokyo.ac.jp DOI: 10.1557/jmr.2016.366

respectively. Figure 1(b) shows the  $6\lambda$  values calculated for Si, carbon nanotubes (CNT), bilayer graphene, and MoS<sub>2</sub>, where the contribution of the tunneling effect is neglected. N is defined as the effective gate number: N = 1 for planar, N = 2 for dual gate, N = 3 for FIN-FET, and N = 4 for gate-all-around. Although the FIN structure has already been adopted for Si to reduce the short channel effects, 4 it is difficult to avoid the short channel effects for channel lengths shorter than 10 nm. 2D layered channels in FET applications are attractive because of their rigidly controllable atomic thickness  $(t_{\rm ch} < 1 \text{ nm})$  and their low dielectric constants where  $\varepsilon_{\rm ch} = \sim 4$  for a typical 2D layered channel.<sup>3,4</sup> This results in a  $6\lambda$  smaller than that of Si. Of course, Si channels of a few nanometers thick have already been constructed using the microfabrication process. However, the operation of Si-MOSFET with an atomic scale thickness is not realistic because the mobility is drastically reduced because of fabrication damage.<sup>5,6</sup> The advantage of 2D materials is their intrinsic atomic thickness, <sup>7,8</sup> which allows both the reduction of the short channel effect and

FIG. 1. (a) The charge conservation model for Si-MOSFETs.<sup>1</sup> (b)  $6\lambda$  for Si, CNT, bilayer graphene and MoS<sub>2</sub>.  $t_{ch} = 5$  nm for Si, and  $t_{ch} = 1$  nm for all other channel materials. Although Poisson's equation in cylindrical co-ordinates should be solved for CNT, the present expression (N = 4) was used for simplicity. (c) Electron effective mass for 2D materials.<sup>9</sup>

the possible retention of high mobility. For the short channel devices in which quasiballistic transport is assumed, the on-current can be determined not by the mobility but by the effective mass. Figure 1(c) shows effective masses  $(m^*)$  for 2D materials. Although there are many 2D channels, bilayer graphene has the lowest effective mass. Therefore, bilayer graphene with an electrostatically tunable band gap still has an advantage over the high performance device.

#### II. GATE STACK FORMATION FOR 2D CHANNELS

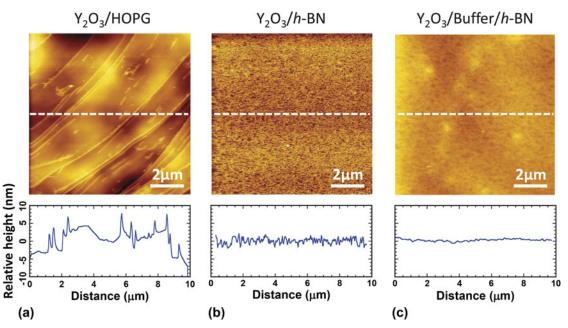

One of the most important building blocks for an FET is the gate stack formation because the device performance is mainly controlled by the carriers that flow near the channel/insulator interface. This is especially true of graphene, which has an atomic monolayer composed of a strong  $sp^2$  hybrid orbital. The defects introduced in graphene during the top gate insulator formation results in the severe degradation of the electron transport properties. Many deposition methods were tested during the initial stages of graphene gate stack research. 10 The obstacles specific to each deposition method have been elucidated. Physical vapor deposition (PVD) methods using high particle energy, such as radio frequency sputtering <sup>10,11</sup> and pulsed laser deposition, <sup>10</sup> introduce a significant amount of defects in graphene. Most of the deposition techniques applicable to the conventional Si process are not applicable to graphene. On the other hand, atomic layer deposition (ALD)<sup>12</sup> has difficulties with nucleation because the graphene surface is chemically inert. Therefore, as shown in Fig. 2(a), Y<sub>2</sub>O<sub>3</sub> is deposited only

on defects and grain boundaries in highly oriented pyrolytic graphite (HOPG) by ALD. These issues have been overcome by the utilization of PVD<sup>13–16</sup> with particle energies lower than that required to displace one C atom out of graphene [ $\sim$ 7.5 eV (Refs. 17 and 18)] and by the utilization of buffer layers such as thin oxidized metal layers, <sup>19</sup> polymer coating, <sup>20</sup> or other types of materials <sup>12,21–23</sup> for ALD. In this case, no defect is introduced. Interestingly, as shown in Fig. 2(b), Y<sub>2</sub>O<sub>3</sub> was deposited directly on approximately 70% of the *h*-BN surface without any preferences for the grain boundaries or defects due to the physical adsorption of the Y precursor from the polarization in *h*-BN. This is the big difference between graphene and other compound type 2D materials. Further utilization of a buffer layer results in the full surface coverage of ALD-Y<sub>2</sub>O<sub>3</sub> with a small surface roughness of approximately 0.2 nm, as shown in Fig. 2(c). <sup>24</sup>

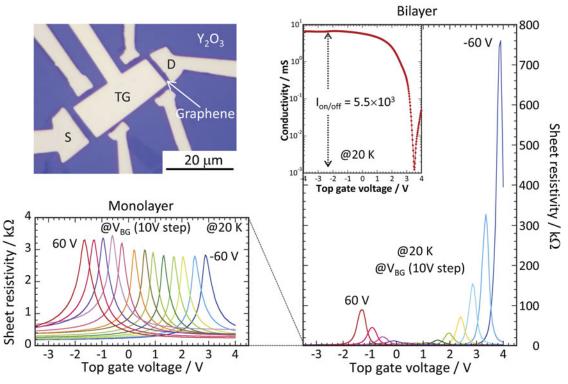

Using an alternative technique to ALD, we have succeeded the high insulating properties of high-k Y<sub>2</sub>O<sub>3</sub> top-gate in graphene FETs by depositing Y metal in an O<sub>2</sub> atmosphere and subsequently applying high-pressure O<sub>2</sub> annealing (100 atm). Y metal was selected because it has the highest susceptibility to oxidation given the thermodynamic considerations. Figure 3 shows the sheet resistivity of monolayer and bilayer graphene as a function of top gate voltage ( $V_{TG}$ ) for different back gate voltages ( $V_{BG}$ ), respectively. These devices were fabricated on SiO<sub>2</sub> (~90 nm)/ $n^+$ -Si substrates by the mechanical exfoliation of Kish graphite. For monolayer graphene, as expected from the linear dispersion without the band gap ( $E_G$ ), ambipolar characteristics are clearly observed. Moreover, because the

FIG. 2. AFM images for (a)  $Y_2O_3$  on HOPG, (b)  $Y_2O_3$  on h-BN, and (c)  $Y_2O_3$  on h-BN with an oxidized Y metal buffer layer of 1.5 nm. The bottom figures show the relative height profiles along the dotted lines in the AFM images.

FIG. 3. Sheet resistivity as a function of  $V_{TG}$  at different  $V_{BG}$  for monolayer and bilayer graphene. An SEM image for typical  $Y_2O_3$  top gate graphene FET is also shown.

electric structure of monolayer graphene is not affected by the external electrical field, the Dirac point is shifted in parallel. This is dependent on the position of the Fermi energy  $(E_{\rm F})$  controlled by the capacitive coupling between the top gate and back gate insulators. On the other hand, the electric structure of bilayer graphene can be tuned and  $E_G$  is opened up to  $\sim 0.3$  eV by increasing the external electrical field. In the tight binding model for bilayer graphene, the origin for the gap opening can be explained by the

breaking of inversion symmetry of two layers, <sup>27,28</sup> that is, the introduction of the potential difference between two layers. In other words, under the external perpendicular electrical field, bilayer graphene can be regarded as parallel plate capacitor with the vacuum as a dielectric. The displacement field  $(\bar{D})^{29}$  is defined as  $\bar{D}=1/2\left[\epsilon_{\rm BG}/d_{\rm BG}(V_{\rm BG}-V_{\rm BG}^0)-\epsilon_{\rm TG}/d_{\rm TG}(V_{\rm TG}-V_{\rm TG}^0)\right]$ in this study, where  $\varepsilon_{\rm BG}$ ,  $\varepsilon_{\rm TG}$ ,  $d_{\rm BG}$ , and  $d_{\rm TG}$  are the dielectric constants, the insulator thickness for back- and top-gate insulators, respectively.  $(V_{\mathrm{TG}}^0,\ V_{\mathrm{BG}}^0)$  is the charge neutrality point to give the minimum resistance in the top-gated region. Indeed, the rapid increase in the sheet resistivity at the Dirac point is clearly observed, which indicates the band gap opening. Comparing the resistivity modulation of monolayer to bilayer graphene is possible because the channel shape factor is removed in the sheet resistivity. The drastic increase in the sheet resistivity for bilayer graphene is quite evident. The maximum current on/off ratio achieved is  $5.5 \times 10^3$  at 20 K, which is the best result at 20 K. The remaining task is to improve the current on/off ratio at room temperature, because it is still  $\sim 100$  at present.  $^{30-32}$ So far,  $E_G$  has been estimated from the temperature dependence of the resistivity at the Dirac point. The detailed analysis on the temperature dependence of the resistivity can be found in the Ref. 26, while in the present paper  $E_G$  will be estimated from the  $C_Q$ measurement in the next section.

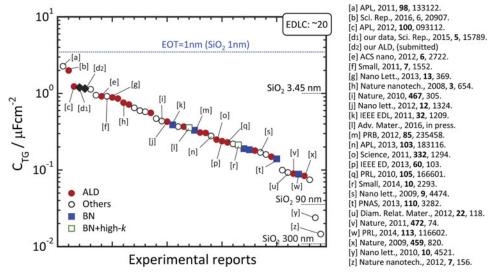

From the viewpoint of miniaturization in device applications, improving the capacitance of the top gate insulator ( $C_{\rm TG}$ ) is critical. Figure 4 shows the  $C_{\rm TG}$  reported so far for graphene FETs in the literature. It should be noted that these data were obtained only

from monolayer, bilayer, and trilayer graphene channels except other 2D materials because the electrical quality of the gate insulator largely depends on the channel materials. The large capacitance is achieved by the direct deposition of a high-k insulator on the graphene, and the capacitance data for h-BN top gate insulators is generally low because of the small dielectric constant of  $\sim$ 3. At present, all the reported data do not reach the effective oxide thickness (EOT) of 1 nm, which is a standard value for Si FETs. Although high temperature annealing (500-600 °C) is required to improve the electrical quality of high-k insulators, such a high temperature annealing introduces defects in graphene. To overcome the oxidation issue for high-k insulators, the combination of h-BN and high-k oxide is key because the oxidation barrier of h-BN is quite high (>800 °C).  $^{33,34}$ As shown in Fig. 2(c), high-k oxide deposition on h-BN using ALD has already been achieved. 24,35 However,  $C_{\rm TG}$  for high-k on h-BN is still low due to the thickness of h-BN,  $^{36,37}$  as shown in Fig. 4. Monolayer h-BN should be used to increase the total capacitance.  $^{24}$

# III. DOS DETERMINATION BY QUANTUM CAPACITANCE MEASUREMENT

In Sec. II, we have observed the carrier modulation in graphene using the electric field effect, although monolayer and bilayer graphene are categorized as metals from the viewpoint of the band structure. This is because the carrier density induced by the back gate  $(n=1/e\ C_{\rm BG}V_{\rm BG})$  becomes larger than that of graphene due to the small DOS near  $E_{\rm F}$ . The DOS—energy relation is quite useful because it can answer the

FIG. 4. Comparison of  $C_{TG}$  with the previously reported values for monolayer, bilayer and trilayer graphene. Closed and open circles indicate that the  $C_{TG}$  was obtained for oxide insulators deposited via ALD and for insulators prepared using another technique, respectively. Closed and open boxes indicate the  $C_{TG}$  obtained for h-BN and for the combination of h-BN and high-k oxide. "EOT = 1 nm" indicates  $C_{TG}$  obtained for SiO<sub>2</sub> with the thickness of 1 nm "EDLC" means an electric double-layer capacitor, whose capacitance value is typically  $\sim 20 \,\mu\text{F/cm}^2$ .

following two questions: Is the linear dispersion really preserved when graphene is sandwiched by the SiO<sub>2</sub>/Si substrate and high-k oxide insulator or is in contact with the metal electrode? Is the  $E_{\rm G}$  formation in bilayer graphene revealed by DOS? However, it is generally difficult to extract the DOS from the I-V characteristics because the contribution of the scattering factor in the Boltzmann transport equation is often unknown. On the other hand, it is possible to extract the DOS by analyzing the  $C_{\rm Q}$  obtained in the C-V measurement. Next we discuss the electric band structure of graphene embedded in the FET structure.

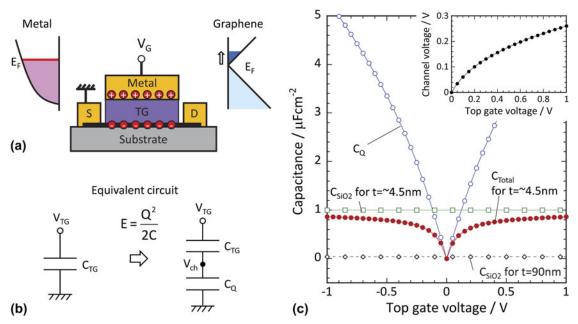

Figure 5(a) gives a schematic drawing to help explain the contribution of  $C_{\rm O}$  to the total capacitance ( $C_{\rm Total}$ ). Graphene, the top gate electrode, and the top gate insulator work as a parallel plate capacitor when voltage is applied between the source and the top gate. A certain density of positive carriers are induced in the top gate electrode, and the equivalent density of negative carriers are induced in the graphene. Here, from the energy viewpoint, DOS at  $E_{\rm F}$  is large for the metal, so there is almost no change in  $E_F$ . On the other hand,  $E_F$  should be shifted upward to induce carriers in graphene because of the small DOS at  $E_{\rm F}$ . The energy required to induce carriers can be modeled using the additional voltage drop  $(V_{ch})$  in the equivalent circuit model, as shown in Fig. 5(b). Because the carriers are "accumulated" in graphene, the circuit element for this voltage drop is a capacitor, not a resistor, or inductor. This is known as the quantum capacitance.<sup>38</sup> In this simple circuit,  $C_{\text{Total}}$  can be described by equation  $1/C_{\text{Total}} = 1/C_{\text{ox}} + 1/C_{\text{Q}}$ , where  $C_{\text{ox}}$  is the geometric capacitance and  $C_{\text{Q}} = e^2$  DOS.<sup>38</sup> Here, the DOS for monolayer and bilayer graphene are  $2E_{\rm F}/\pi(\nu_{\rm F}\hbar)^{41}$  and  $m*/2\pi\hbar,^{28,41}$  respectively.  $\nu_{\rm F}$  is the Fermi velocity (1  $\times$  10<sup>8</sup> cm/s) and  $\hbar$  is the Planck's constant. Here, let's estimate  $C_Q$  and  $C_{Total}$  for monolayer graphene when  $C_{\text{ox}} = 1 \,\mu\text{F/cm}^2$  for the SiO<sub>2</sub> thickness of 4.5 nm. The key is the calculation of  $V_{\rm ch}$  in Fig. 5(b), because  $C_{\rm Q}$  is a function of  $V_{\rm TG}$ .  $V_{\rm ch}$  can be expressed as  $V_{\rm ch} = V_{\rm ch} = \int_0^{V_{\rm TG}} C_{\rm Total}/C_{\rm ox} dV_{\rm TG}$  from the equivalent circuit.  $E_{\rm F}$  is indeed the charging energy and is expressed as  $E_{\rm F} = eV_{\rm ch}$ . As a result,  $C_{\rm Q}$  can be estimated since  $C_{\rm Q}$  is a function of  $E_F$ . Figure 5(c) shows  $C_{ox}$ ,  $C_O$ , and  $C_{Total}$  as a function of top gate voltage.  $C_{\rm O}$  increases as  $E_{\rm F}$  increases for monolayer graphene, while  $C_{SiO_2}$  is constant. As a result,  $C_{\text{Total}}$  depends on  $V_{\text{TG}}$ . For comparison,  $C_{\text{SiO}_2}$  $(\sim 0.0383 \ \mu \text{F/cm}^2)$  for the SiO<sub>2</sub> thickness of 90 nm (this is a typical thickness for back gate SiO<sub>2</sub>) is also plotted, suggesting that the contribution of  $C_{\rm O}$  in  $C_{\rm Total}$  can be neglected because of the small  $C_{SiO_2}$  value. Therefore, we do not generally discuss  $C_{\rm O}$  for back gate graphene devices. In other words, to extract  $C_Q$ , a top gate graphene device with a  $C_{TG}$  value comparable to the  $C_{\rm O}$  value is critical, which indicates the importance of the gate stack formation in Sec. II. On the other hand, from the device operation viewpoint, a large contribution of  $C_Q$  in  $C_{Total}$  means that inducing carriers in graphene is difficult. The inset in Fig. 5(c) shows the channel voltage  $(V_{ch})$  calculated as a function of  $V_{TG}$ .  $V_{\rm ch}$  is the voltage drop equivalent to the energy required

FIG. 5. (a) Schematic drawing of the graphene device and DOSs for metal and monolayer graphene. (b) Equivalent circuits with and without  $C_{\rm Q}$ . (c) Capacitance as a function of  $V_{\rm TG}$ .  $C_{\rm SiO_2}$  for the SiO<sub>2</sub> thickness of 4.5 nm,  $C_{\rm Q}$  for monolayer graphene and their total capacitance  $(C_{\rm Total})$  are shown. For comparison,  $C_{\rm SiO_2}$  for the SiO<sub>2</sub> thickness of 90 nm is also indicated. Inset: Channel voltage  $[V_{\rm ch}$  in (b)] as a function of  $V_{\rm TG}$ .

to induce carriers in graphene. Thus, when  $V_{\rm TG}=1~\rm V$  is applied,  $\sim 30\%$  of  $V_{\rm TG}$  is spent in graphene itself and the actual voltage applied to the top gate insulator is reduced to be  $V=V_{\rm TG}-V_{\rm ch}$ . This is a common problem for highmobility channels. However, consider  $C_{\rm Q}$  positively as it can be the analytical tool used to extract DOS by the C-V measurement.

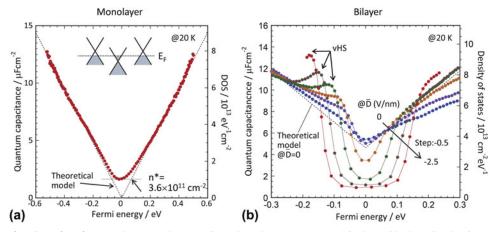

Figure 6 shows the  $C_Q$  extracted from the C-V measurements for (a) monolayer graphene and (b) bilayer graphene, respectively.<sup>25,26</sup> It should be noted that the vertical axis on the right side is converted from  $C_0$  to DOS using the relation of  $C_Q = e^2$  DOS. The devices used in this analysis are the same as those in Fig. 3. For monolayer graphene, the estimated  $C_{\rm O}$  value is consistent with the theoretical dotted line values for  $E_{\rm F} > \sim 0.15$  eV. The deviation from the theoretical value near the Dirac point is due to the residual carriers that are externally induced by the charged impurities. 14,40,42 The residual carrier density  $(n^*)$ , as shown by the arrow in Fig. 6(a) is calculated as  $3.6 \times 10^{11}$  cm<sup>-2</sup> using the relation of  $E_{\rm F} = \hbar v_{\rm F} \sqrt{\pi n^*}$ , where  $\hbar$  is the reduced Planck constant and  $v_F$  is the Fermi velocity. The  $n^*$  values obtained from the C-V and I-V measurements are almost identical. Based on these results, it has been shown that graphene sandwiched between Y<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> generally preserves the linear band structure with the exception being near the Dirac point. Although the electric band structure is generally determined experimentally by an angle-resolved photoemission spectroscopy (ARPES), <sup>43</sup> the energy resolution in DOS obtained using the  $C_{\rm O}$  measurement is much higher than that by ARPES for the energy range of actual device operation.

On the other hand, the  $E_{\rm G}$  formation (for bilayer graphene), where DOS becomes nearly zero, is clearly observed by increasing the displacement field  $(\bar{D})$ . The equation for  $\bar{D}$  is provided in the previous section.

$E_{\rm G}$  is defined as the energy between inflection points for the conduction and valence sides in Fig. 6(b).  $E_{\rm G}$  is roughly  $\sim 0.3$  V at  $\bar{D}=2.5$  V/nm,  $^{26}$  which corresponds to the maximum value expected from the theoretical calculation. It should be emphasized that the DOS within the gap region almost reaches zero, which is not observed in the previous report for bilayer graphene with the h-BN top gate. Moreover, the van Hove Singularity is also observed near the valence band edge, as shown by arrows. In the case of the I-V measurement, the temperature dependence of the resistivity at the Dirac point must be measured to determine  $E_{\rm G}$ . However,  $E_{\rm G}$  can be determined directly from the  $C_{\rm Q}$  measurement because the scattering factor is not included in the C-V measurement.

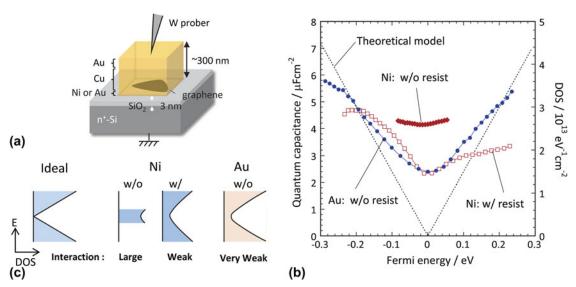

Finally, the application of the  $C_{\rm O}$  measurement to the metal/graphene contact in the graphene FET is described.<sup>45</sup> In terms of electron device miniaturization, the electrical contacts are critically important to reduce the total resistance. 46 This is more significant in the higher carrier mobility channel. Although no Schottky barrier exists at the graphene/metal interface due to the lack of a band gap, the contact resistivity is intrinsically high due to the small DOS in graphene. 46 It is known that the DOS of monolayer graphene increases with contact to the metal due to the orbital hybridization, that is,  $\pi - d$ coupling.<sup>47</sup> The typical chemisorption group is Ni, while the typical physisorption group is Au. 48 Here, our strategy is the reduction of the contact resistivity by the  $\pi - d$  coupling with Ni. For this purpose, the DOS of graphene in contact with the metals should be estimated through the  $C_{\rm O}$  measurement. Figure 7(a) shows the schematic drawing of the experimental setup. The thickness of the back gate SiO<sub>2</sub> in the metal/ graphene/SiO<sub>2</sub>/n<sup>+</sup>-Si contact structure is reduced to  $\sim$ 3 nm to extract the  $C_{\rm O}$ . Even for  $\sim$ 3 nm thickness of

FIG. 6. (a)  $C_Q$  as a function of  $E_F$  for monolayer graphene.  $E_F$  is evaluated as  $E_F = eV_{ch}$ .  $n^*$  is the residual carrier density. Inset: The schematic drawing shows that the spatial distribution of charged impurities results in the variation of the Dirac point. (b)  $C_Q$  as a function of  $E_F$  for bilayer graphene. The  $E_F$  formation is clearly observed as the external electrical field is increased.

FIG. 7. (a) Schematic of the metal/graphene/SiO<sub>2</sub>/ $n^+$ -Si device to extract  $C_Q$  for metal/graphene structure. The thickness of SiO<sub>2</sub> is reduced to 3 nm, which results in a  $C_{SiO_2}$  comparable to  $C_Q$ . (b) The experimentally extracted  $C_Q$  of graphene in contact with metals. Solid red circle, open red rectangular, and solid blue circle represent the resist-processed Ni, resist-free Ni, and resist-free Au devices, respectively. (c) Summary of DOS—energy relation after the metal/graphene interaction suggested from the  $C_Q$  measurements.

SiO<sub>2</sub>, monolayer graphene can be identified by the optical contrast under the optical microscope, which is supported by our calculation on the visibility of graphene on SiO<sub>2</sub>. The key technique used here is the resist-free metal deposition process using the finely patterned PMMA shadow masks, which enables us to extract the "intrinsic" metal/graphene interaction. Many researchers have reported that the resist residue remains on graphene. <sup>49–51</sup> The resist residue is a serious concern in light of the fact that activated carbon, whose hydrophobic surface attracts organic materials, is composed of graphene.<sup>52</sup> Fig. 7(b) shows the DOS extracted from the  $C_{\rm O}$  measurements. For the resist-free metal/graphene contacts, graphene underneath the Au electrode maintains the linear DOS—energy relation except near the Dirac point, while the DOS of graphene underneath the Ni electrode is broken and largely enhanced around the Dirac point, resulting in only a slight modulation of the Fermi energy in the graphene. On the other hand, when Ni is deposited using the polymer resist, the traces of linear dispersion of the graphene can be observed, which is also seen in the I-V curve. <sup>53</sup> Fig. 7(c) summaries the DOS—energy relation for monolayer graphene modified with the metal contact. The contact resistivity measurements using the resist-free metal deposition technique show that the contact resistivity obtained for the Ni electrode has been reduced to  ${\sim}1500~\Omega$   $\mu m$  because of the increase in the DOS by the  $\pi - d$  coupling.<sup>45</sup> Although this contact resistivity value is still high for the requirement, the present experiment clearly suggest that one of effective guidelines to reduce the contact resistivity is the increase in the DOS of graphene underneath the metal electrode.

#### IV. CONCLUSIONS

In this paper, we have discussed the gate stack formation in graphene FETs and the extraction of DOS through  $C_{\rm Q}$  measurements. The top gate formation, which appears at first glance to be quite easy, is actually very difficult because defects are easily introduced in graphene by the conventional deposition techniques for high-k oxides. The improvement of the gate stack process in graphene research enables the extraction of DOS through the  $C_{\rm Q}$  measurement. It is shown that the electric band structure of graphene in contact with gate insulators or metal electrode deviates from the intrinsic band gap structure. Through the extension of this technique, a further understanding of the graphene/insulator and the graphene/metal interfaces is needed to fabricate graphene FETs.

#### **ACKNOWLEDGMENTS**

We are grateful to Covalent Materials for kindly providing the Kish graphite and to Drs T. Taniguchi and K. Watanabe of the National Institute of Materials Science (NIMS) for kindly providing the *h*-BN crystals. This research was partly supported by JSPS KAKENHI Grant Numbers JP25107004, JP16H04343, and JP16K14446.

#### **REFERENCES**

- 1. S.M. Sze and K.K. Ng: *Physics of Semiconductor Devices* (Wiley-Interscience, NJ, 2007).

- I. Ferain, C.A. Colinge, and J-P. Colinge: Mutligate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. *Nature* 479, 310 (2011).

- R-H. Yan, A. Ourmazd, and K.F. Lee: Scaling the Si MOSFET: From bulk to SOI to bulk. *IEEE Trans. Electron Devices* 39, 1704 (1992).

- 4. M. Bohr: The evolution of scaling from the homogeneous era to the heterogeneous era. *IEDM Tech. Dig.* 978 (2011).

- L. Gomez, I. Aberg, and J.L. Hoyt: Electron transport in strainedsilicon directly on insulator ultrathin-body n-MOSFETs with body thickness ranging from 2 to 25 nm. *IEEE Trans. Electron Device Lett.* 28(4), 285 (2007).

- R. Granzner, V.M. Polyakov, C. Schippel, and F. Schwierz: Empirical model for the effective electron mobility in silicon nanowires. *IEEE Trans. Electron Devices* 61(11), 3601 (2014).

- F. Schwierz: Graphene transistors. Nature Nanotechnol. 5, 487 (2010).

- S.Z. Butler, S.M. Hollen, L. Cao, Y. Cui, J.A. Gupta, H.R. Gutiérrez, T.F. Heinz, S.S. Hong, J. Huang, A.F. Ismach, E. Johnston-Halperin, M. Kuno, V.V. Plashnitsa, R.D. Robinson, R.S. Ruoff, S. Salahuddin, J. Shan, L. Shi, M.G. Spencer, M. Terrones, W. Windl, and J.E. Goldberger: Progress, challenges, and opportunities in two-dimensional materials beyond graphene. ACS Nano 7(4), 2898 (2013).

- W. Zhang, Z. Huang, W. Zhang, and Y. Li: Two-dimensional semiconductors with possible high room temperature mobility. *Nano Res.* 7(12), 1731 (2014).

- Z.H. Ni, H.M. Wang, J. Kasim, Y.H. Wu, and Z.X. Shen: Tunable stress and controlled thickness modification in graphene by annealing. ACS Nano 2(5), 1033 (2008).

- Z. Jin, Y. Su, J. Chen, X. Liu, and D. Wu: Study of AlN dielectric film on graphene by Raman microscopy. *Appl. Phys. Lett.* 95, 233110 (2009).

- X. Wang, S.M. Tabakman, and H. Dai: Atomic layer deposition of metal oxides on pristine and functionalized graphene. *J. Am. Chem. Soc.* 130, 8152 (2008).

- Z. Wang, H. Xu, Z. Zhang, S. Wnag, L. Ding, Q. Zeng, L. Yang,

T. Pei, X. Liang, M. Gao, and L-M. Peng: Growth and performance of yttrium oxide as an ideal high-k gate dielectric for carbon-based electronics. *Nano Lett.* 10, 2024 (2010).

- L.A. Ponomarenko, R. Yang, R.V. Gorbachev, P. Blake, A.S. Mayorov, K.S. Novoselov, M.I. Katsnelsonm, and A.K. Geim: Density of states and zero Landau level probed through capacitance of graphene. *Phys. Rev. Lett.* 105, 136801 (2010).

- H. Miyazaki, K. Tsukagoshi, A. Kanda, M. Otani, and S. Okada: Influence of disorder on conductance in bilayer graphene under perpendicular electric field. *Nano Lett.* 10, 3888 (2010).

- K. Nagashio, T. Nishimura, and A. Toriumi: Estimation of residual carrier density near the Dirac point in graphene through quantum capacitance measurement. *Appl. Phys. Lett.* 102, 173507 (2013).

- C-T. Chen, E.A. Casu, M. Gajek, and S. Raoux: Low-damage high-throughput grazing-angle sputter deposition on graphene. *Appl. Phys. Lett.* 103, 033109 (2013).

- O. Lehtinen, J. Kotakoski, A.V. Krasheninnikov, and J. Keinonen: Cutting and controlled modification of graphene with ion beams. *Nanotechnology* 22, 175306 (2011).

- S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S.K. Banerjee: Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric. *Appl. Phys. Lett.* 94, 062107 (2009).

- D.B. Farmer, H.Y. Chiu, Y.M. Lin, K.A. Jenkins, F.N. Xia, and P. Avouris: Utilization of a buffered dielectric to achieve high field-effect carrier mobility in graphene transistor. *Nano Lett.* 9, 4474 (2009).

- J.R. Williams, L. DiCarlo, and C.M. Marcus: Quantum hall effect in a gate-controlled p-n junction of graphene. *Science* 317, 638 (2007).

- J.M.P. Alaboson, Q.H. Wang, J.D. Enery, A.L. Lipson, M.J. Bedzyk, J.W. Elam, M.J. Pellin, and M.C. Hersam: Seeding atomic layer deposition of high-k dielectrics on epitaxial graphene with organic self-assembled monolayers. ACS Nano 5, 5223 (2011)

- S. Jandhyala, G. Mordi, B. Lee, G. Lee, C. Floresca, P-R. Cha, J. Ahn, R.M. Wallace, Y.J. Chabal, M.J. Kim, L. Colombo, K. Cho, and J. Kim: Atomic layer deposition of dielectrics on graphene using reversibly physisorbed ozone. ACS Nano 6, 2722 (2012).

- 24. N. Takahashi, K. Watanabe, T. Taniguchi, and K. Nagashio: Atomic layer deposition of high-k Y<sub>2</sub>O<sub>3</sub> on h-BN for a gate stack in graphene FETs. *Nanotechnology* **26**, 175708 (2015).

- K. Kanayama, K. Nagashio, T. Nishimura, and A. Toriumi: Large Fermi energy modulation in graphene transistors with high-pressure O<sub>2</sub>-annealed Y<sub>2</sub>O<sub>3</sub> topgate insulators. *Appl. Phys. Lett.* **104**, 083519 (2014).

- K. Kanayama and K. Nagashio: Gap state analysis in electric-fieldinduced band gap for bilayer graphene. Sci. Rep. 5, 15789 (2015).

- E. McCann: Asymmetry gap in the electronic band structure of bilayer graphene. *Phys. Rev. B: Condens. Matter Mater. Phys.* 74, 161403(R) (2006).

- M. Koshino: Electronic transport in bilayer graphene. New J. Phys. 11, 095010 (2009).

- Y. Zhang, T-T. Tang, C. Girit, Z. Hao, M.C. Martin, A. Zettl, M.F. Crommie, Y.R. Shen, and F. Wang: Direct observation of a widely tunable bandgap in bilayer graphene. *Nature* 459, 820 (2009).

- F. Xia, D.B. Farmer, Y-M. Lin, and P. Avouris: Graphene fieldeffect transistors with high on/off current ratio and large transport band gap at room temperature. *Nano Lett.* 10, 715 (2010).

- T. Chu and Z. Chen: Achieving large transport bandgaps in bilayer graphene. *Nano Res.* 8(10), 3228 (2015).

- N. Takahashi and K. Nagashio: Buffer layer engineering on graphene via various oxidation methods for atomic layer deposition. (submitted).

- Z. Liu, Y. Gong, W. Zhou, L. Ma, J. Yu, J.C. Idrobo, J. Jung, A.H. MacDonald, R. Vajtai, J. Lou, and P.M. Ajayan: Ultrathin high-temperature oxidation-resistant coatings of hexagonal boron nitride. *Nat. Commun.* 4, 2541 (2013).

- L.H. Li, J. Cervenka, K. Watanabe, T. Taniguchi, and Y. Chen: Strong oxidation resistance of atomically thin boron nitride nanosheets. ACS Nano 8, 1457 (2014).

- 35. H. Liu, K. Xu, and P.D. Ye: The integration of high-*k* dielectric on two-dimensional crystals by atomic layer deposition. *Appl. Phys. Lett.* **100**, 152115 (2012).

- Q. Han, B. Yan, T. Gao, Y. Zhang, Z. Liu, X. Wu, and D. Yu: Boron nitride film as a buffer layer in deposition of dielectrics on graphene. *Small* 10, 2293 (2014).

- 37. X. Zou, C-W. Huang, L. Wang, L-J. Yin, W. Li, J. Wang, B. Wu, Y. Liu, Q. Yao, C. Jiang, W-W. Wu, L. He, S. Chen, J.C. Ho, and L. Liao: Dielectric engineering of a boron nitride/hafnium oxide heterostructure for high-performance 2D field effect transistors. *Adv. Mater.* 28, 2062 (2016).

- S. Luryi: Quantum capacitance devices. Appl. Phys. Lett. 52, 501 (1988).

- 39. T. Fang, A. Konar, H. Xing, and D. Jena: Carrier statistics and quantum capacitance of graphene sheets and ribbons. *Appl. Phys. Lett.* **91**, 092109 (2007).

- K. Nagashio, T. Nishimura, and A. Toriumi: Estimation of residual carrier density near the Dirac point in graphene through quantum capacitance measurement. *Appl. Phys. Lett.* 102, 173507 (2012).

- A.H. Castro Neto, F. Guinea, N.M. Peres, K.S. Novoselov, and A.K. Geim: The electronic properties of graphene. *Rev. Mod. Phys.* 81, 109 (2009).

- S. Adam, E.H. Hwang, V.M. Galitski, and S. Das Sarma: A selfconsistent theory for graphene transport. PNAS 104, 18392 (2007).

- 43. T. Ohta, A. Bostwick, T. Seyller, K. Horn, and E. Rotenberg: Controlling the electronic structure of bilayer graphene. *Science* **313**, 951 (2006).

- 44. A.F. Young, C.R. Dean, I. Meric, S. Sorgenfrei, H. Ren, K. Watanabe, T. Taniguchi, J. Hone, K.L. Shepard, and P. Kim: Electronic compressibility of layer-polarized bilayer graphene. *Phys. Rev. B: Condens. Matter Mater. Phys.* 85, 235458 (2012).

- R. Ifuku, K. Nagashio, T. Nishimura, and A. Toriumi: The density of states of graphene underneath a metal electrode and its correlation with the contact resistivity. *Appl. Phys. Lett.* 103, 033514 (2013).

- K. Nagashio and A. Toriumi: Graphene/metal contact. In *Frontiers of Graphene and Carbon Nanotubes* (Springer, Tokyo, 2015);

pp. 53–78.

- 47. B. Hammer and J.K. Norskov: Why gold is the noblest of all the metals. *Nature* **376**, 238 (1995).

- G. Giovannetti, P.A. Khomyakov, G. Brocks, V.M. Karpan, J. van der Brink, and P.J. Kelly: Doping graphene with metal contacts. *Phys. Rev. Lett.* 101, 026803 (2008).

- M. Ishigami, J.H. Chen, W.G. Cullen, M.S. Fuhrer, and E.D. Williams: Atomic Structure of Graphene on SiO<sub>2</sub>. *Nano Lett.* 7, 1643 (2007).

- Z. Cheng, Q. Zhou, C. Wang, Q. Li, C. Wang, and Y. Fang: Toward intrinsic graphene surfaces: a systematic study on thermal annealing and wet-chemical treatment of SiO<sub>2</sub>-supported graphene devices. *Nano Lett.* 11, 767 (2011).

- A.M. Goossens, V.E. Calado, A. Barreiro, K. Watanabe, T. Taniguchi, and L.M.K. Vandersypen: Mechanical cleaning of graphene. *Appl. Phys. Lett.* 100, 073110 (2012).

- M. Acharya, M.S. Strano, J.P. Mathews, S.J.L. Billinge, V. Petkov, S. Subramoney, and H.C. Foley: Simulation of nanoporous carbons: a chemically constrained structure. *Philos. Mag. B* 79, 1499 (1999).

- A.D. Bartolomeo, F. Giubileo, F. Romeo, P. Sabatino, G. Carapella, L. Iemmo, T. Schroeder, and G. Lupina: Graphene field effect transistors with niobium contacts and asymmetric transfer characteristics. *Nanotechnology* 26, 475202 (2015).